Product Summary

The XC2S300E-6PQG208C is a member of the Spartan-IIE Field-Programmable Gate Array family, which gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The seven-member family offers densities ranging from 50,000 to 600,000 system gates. System performance is supported beyond 200 MHz. The XC2S300E-6PQG208C features include block RAM (to 288K bits), distributed RAM (to 221,184 bits), 19 selectable I/O standards, and four DLLs (Delay-Locked Loops). Fast, predictable interconnect means that successive design iterations continue to meet timing requirements. The XC2S300E-6PQG208C is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

Parametrics

XC2S300E-6PQG208C absolute maximum ratings: (1)VCCINT, Supply voltage relative to GND: –0.5 to 2.0 V; (2)VCCO, Supply voltage relative to GND: –0.5 to 4.0 V; (3)VREF, Input reference voltage: –0.5 to 4.0 V; (4)VIN, Input voltage relative to GND: –0.5 to 4.0 V; (5)VTS, Voltage applied to 3-state output: –0.5 to 4.0 V; (6)TSTG, Storage temperature (ambient): –65 to +150℃; (7)TJ, Junction temperature: +125℃.

Features

XC2S300E-6PQG208C features: (1)Second generation ASIC replacement technology; (2)SelectRAM hierarchical memory; (3)Fully 3.3V PCI compliant to 64 bits at 66 MHz and CardBus compliant; (4)Lowpower segmented routing architecture; (5)Dedicated carry logic for highspeed arithmetic; (6)Efficient multiplier support; (7)Cascade chain for wideinput functions; (8)Abundant registers/latches with enable, set, reset; (9)Four dedicated DLLs for advanced clock control; (10)Four primary lowskew global clock distribution nets; (11)IEEE 1149.1 compatible boundary scan logic; (12)Pbfree package options; (13)Lowcost packages available in all densities; (14)Family footprint compatibility in common packages; (15)19 highperformance interface standards; (16)Up to 205 differential I/O pairs that can be input, output, or bidirectional; (17)Hot swap I/O (CompactPCI friendly); (18)Core logic powered at 1.8V and I/Os powered at 1.5V, 2.5V, or 3.3V; (19)Fully supported by powerful Xilinx ISE development system.

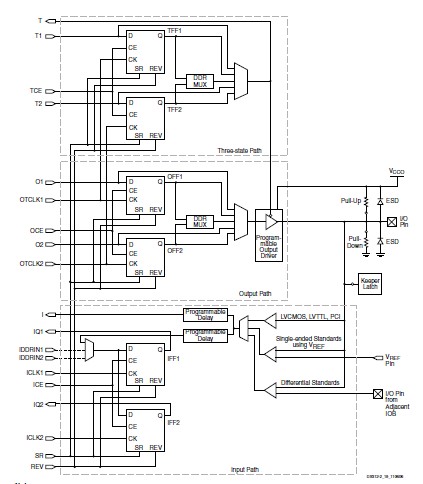

Diagrams

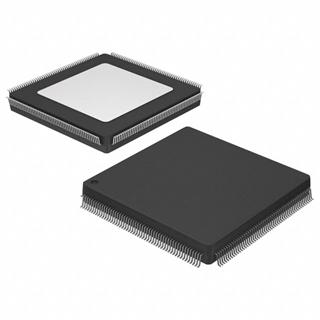

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

XC2S300E-6PQG208C |

|

IC SPARTAN-IIE FPGA 300K 208PQFP |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

XC2S100 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XC2S100-5FG256C |

|

IC FPGA 2.5V 600 CLB'S 256-FBGA |

Data Sheet |

|

|

||||||

|

XC2S100-5FG256I |

|

IC FPGA 2.5V I-TEMP 256-FBGA |

Data Sheet |

|

|

||||||

|

XC2S100-5FG456C |

|

IC FPGA 2.5V 600 CLB'S 456-FBGA |

Data Sheet |

|

|

||||||

|

XC2S100-5FG456I |

|

IC FPGA 2.5V I-TEMP 456-FBGA |

Data Sheet |

Negotiable |

|

||||||

|

XC2S100-5FGG256C |

|

IC SPARTAN-II FPGA 100K 256-FBGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))